# 4-9 FPGA を用いた電場観測用デジタル信号処理部の基礎開発

石坂研究室 1915084 山崎 有生

### 1. はじめに

本研究では、これまで本研究室で開発されてきたアナログ方式電場観測装置が多くのアナログ素子を使用することにより、装置の容積、容量が大きくなってしまう問題を解決するために、FPGAを用いて装置のデジタル化を目指す。装置のデジタル化に関しての先行研究が行われたが、サンプリング周波数500kHzでデータ量が50万点の中で1024点のデータしか抽出することができなかったため、低周波データに対応できない問題が残った。そこで、ロケット実験における電場の観測周波数帯はDC~50Hzより、低周波数帯に対応できる電場観測装置の信号処理部の基礎開発を行う。

### 2. デジタル信号処理部の設計・試作

デジタル式電場観測装置の概要図を図1に示す。 デジタル式電場観測装置は、アナログ回路部とデジ タル回路部で構成される。アナログ回路部は差動増 幅器と LPF で構成される。LPF は信号のサンプリン グを行う際に発生するエイリアスの除去を目的とす る。デジタル回路部では FPGA により信号処理を行 い、観測データを出力する。ここで、本研究では、 デジタル回路部の開発のみを行うことにする。本研 究では、Xilinx社のFPGAを用いて、FPGA内蔵のXADC に取り込まれた信号の高周波成分をデジタルフィル タ(移動平均)により取り除き PC に出力するシステ ムを構築する。フィルタのカットオフ周波数は50Hz とした。また、システムの構築には Xilinx 社が無償 で提供しているハードウェア開発環境である Vivado とソフトウェア開発環境である Vitis を組み 合わせて行う。

## 3. \_\_実験結果

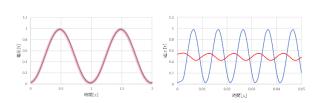

本研究では、信号発生器から 1Hz~100Hz の正 弦波を FPGA に入力することで実験を行った。実 験条件と出力結果を表1と図2に示す。図2の左側より、入力信号が1Hzのときは2つの信号が重ねっており信号の変化は見られない。次に図2の右側を見ると、入力信号がカットオフ周波数である50Hzよりも大きい100Hzのときはフィルタ通過後の信号は大きく減衰しておりLPFとして機能していることが確認できる。

### 4. まとめ

本研究では、FPGAを用いて電場観測用デジタル信号処理部の基礎開発を行い、信号をFPGA内で処理することができた。しかし、信号を出力するシステムとLPFを通すシステムは別のプログラムで作成しており、リアルタイム処理に対応していない。今後は1つのプログラムですべての処理を行えるシステムの構築を目指すと同時に移動平均よりも精度の高いLPFであるFIRフィルタの構築なども目指す。

表 1 実験条件

| 入力信号      | 1Hz, 50Hz, 100Hz              |

|-----------|-------------------------------|

| 入力電圧      | 1Vpp、offset : 0.5V            |

| サンプリング周波数 | 900Hz                         |

| デジタルフィルタ  | 移動平均フィルタ<br>(カットオフ周波数 : 50Hz) |

図1 デジタル式電場観測装置

図 2 出力波形 (青線:入力信号、赤線:フィルタ通 過後の信号、入力信号 左:1Hz、右:100Hz)